| <ol> <li>For non-single layer boards, PCBs should be fabricated with layer</li> </ol> | 1. | For non-single | laver boards | , PCBs should be | e fabricated with | layeı |

|---------------------------------------------------------------------------------------|----|----------------|--------------|------------------|-------------------|-------|

|---------------------------------------------------------------------------------------|----|----------------|--------------|------------------|-------------------|-------|

- a. An Odd Number of

- b. An Even Number of

- c. Any Number of

Reason: Using an odd number of layers may result in board warpage.

- 2. Which of the following is not taken into consideration when calculating the characteristic impedance for each layer?

- a. Trace width

- b. Trace height

- c. Trace length

- d. Distance of the trace to a plane

Reason: The characteristic impedance is a function of the inductance and capacitance. The trace width and height determine inductance. The trace width and distance of the trace to the plane influences the capacitance.

- 3. The declaration of vias-in-pads is determined in the

- a. Assembly Notes

- b. Fabrication Notes

- c. Fabrication Files (ODB++, Gerber, IPC 2582, NC drill)

- d. Via stack up

- e. Layer Stack up

Reason: Via-in-pad is not defined in existing fabrication formats since the formats do not provide guidance on filling a hole after it has been drilled. It must be given as an instruction to the fabrication personnel.

- 4. Select the answer that is true: Mechanical layers...

- a. Are unique to each project

- b. Are only declared in the PCB editor during layout

- c. Follow an IPC standard

- d. Should be consistently used in the footprint libraries for courtyards and assembly files

Reason: A, B and C are false. The IPC does not have a standard for mechanical layers. A company should have its own standard for the mechanical layers and apply it consistently to both the footprint libraries and the PCB layout for any project.

#### 5. Silk Screens

- a. Are not required for every component

- b. Are highly recommended for prototype boards

- c. Should be kept to a minimal for production boards

- d. All of the above

Reason: Silks have traditionally been used for test and rework to help guide those who are performing these tasks. Other than for identification, production boards need little silk screen.

- 6. The use of 3D component models in the PCB layout can assist with the

- a. Electrical clearance rule

- b. Component clearance rule

- c. Silk clearance rule

- d. All the above

Reason: Component clearance rule has to do with mechanical clearances whereas electrical clearances are specific to copper of different nets.

- 7. True or False The solder mask has an impact on the trace impedance.

- a. True

- b. False

Reason: The solder mask is a dielectric material which impacts the capacitance of the trace to the plane.

- 8. When writing a requirement, the following word should be used to denote a requirement:

- a. Should

- b. Would

- c. Can

- d. Shall

- e. May

Reason: 'Shall' has traditionally been used to denote a requirement.

### 9. When writing a requirement

- a. The use of the word "and" is okay

- b. The use of the word "or" is okay

- c. Both of the above

- d. None of the above

Reason: The use of 'and' or 'or' results in a requirement that requires two tests. Requirements should be written so that only one test needs to be performed.

#### 10. A well written requirement

- a. Has a complex sentence structure

- b. Uses technical verbiage

- c. Is testable by its nature

- d. Needs to be vague

Reason: A well written requirement can be tested.

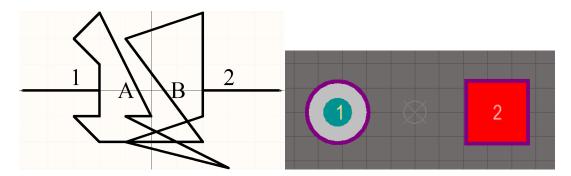

11. Consider the following symbol and corresponding footprint:

The following symbol and corresponding footprint

- a. Are recognized by the EDA tool as a valid component

- b. Would be flagged by the Electrical Rule checker in the schematic tool

- c. Would be flagged by the Design Rule checker in the PCB editor

- d. Both B and C

Reason: Though it may look like a Picasso to the human eye, the symbol pin numbers match the pad numbers.

- 12. When is the earliest time one should communicate the bill of materials?

- a. After fabrication has been started

- b. After the boards have been fabricated

- c. When the schematics are completed

- d. After the layout is complete

Reason: The sooner the bill of material can be reviewed, the better the chances of correcting issues prior to manufacturing. Early review of the BOM after schematic capture is useful for procurement and supply chain availability, but purchasing before the layout is complete is risky. Problems found during layout often cause schematic changes.

- 13. What is the best method to provide a unique identifier for each component in the library?

- a. Use the manufacturer's part number

- b. Use the vendor's part number

- c. Use a part number that is assign by your company

- d. Use a part number that you make up as you go

Reason: The best part numbering scheme is to use a part number that has been assigned by your company. The other methods listed may work; however, there is always a remote possibility that a duplicate number can be introduced.

- 14. During post assembly testing, it was found that a latch on one of the connectors could not be fully extended due to other components located nearby. What would have prevented this situation from occurring?

- a. The use of a 3D component

- b. The use of a 3D component and component clearance rule

- c. The use of a courtyard

- d. The use of a courtyard and a component clearance rule

Reason: Though 3D is extremely useful for fitment, the courtyard takes into consideration the egress that may be needed. The component clearance rule will still be necessary for the vertical height requirement. The 3D body will only take into consideration it physical location, not the egress that may be necessary.

- 15. Though schematic tools do have to use a grid for pin connectivity, in theory, the grid used in a schematic is

- a. In metric (mm)

- b. In imperial (mils)

- c. Both A and B interchangeably

- d. Dimensionless

Reason: Schematics, by their nature are dimensionless.

- 16. The biggest factor when it comes to characteristic impedance is

- a. Clock speed of the board crystal

- b. The integrity of the signal from the output buffer of the sending component

- c. The voltage level

- d. The physical aspects of the board

Reason: The four factors that make up the trace characteristic impedance come from the structure of the board.

- 17. True or False: Microvias are the same as a one-layer blind or buried vias

- a. True

- b. False

Reason: Though blind and buried vias can be limited to one layer, microvias are filled with copper and can be stacked.

- 18. Which of the following drill document(s) must be provided to the fabricator to program their drilling equipment?

- a. Drill Plot

- b. Drill Drawing

- c. NC Drill file

- d. All of the above

Reason: The drill plot and drawing are graphical representations for the human eye; most fab houses use the NC drill file for programming the drills.

- 19. True or False: ODB++ and Gerbers are proprietary formats

- a. True

- b. False

Reason: That's just the way it is! IPC-2581 was specifically released to address this concern.

- 20. The solder paste files are generally produced

- a. In a fabrication file format

- b. Through a manual drawing

- c. As part of the bill of materials

Reason: It is a product of the fabrication file generation.