- Nine Dot Connects

- Webinar of the Month

- Recently Posted Videos

- Altium Designer (70)

- Cabling & Wire Harness (5)

- Design for Manufacturing (10)

- Fabrication & Assembly (9)

- ECAD & MCAD (7)

- High Speed Design (20)

- Library Management (18)

- Vault & Data Management (16)

- PCB Broadview (4)

- PCB Elements (16)

- Power Supplies (5)

- Simulation (12)

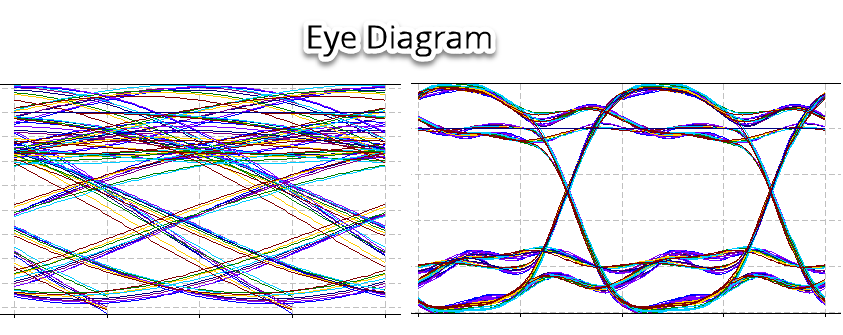

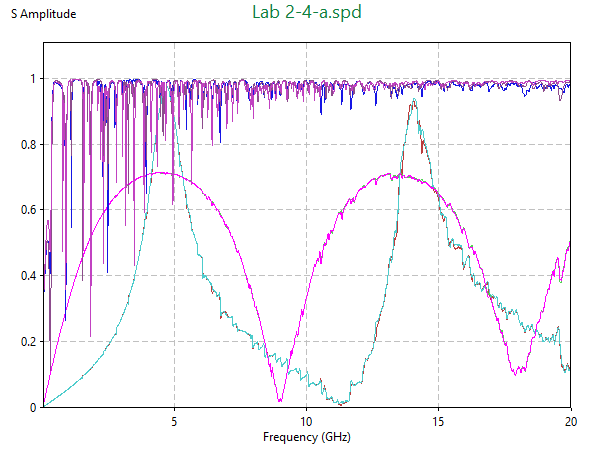

Practical Aspects of Signal Integrity - Part 1

"There are two kinds of engineers: those who have signal integrity problems and those that will." - Eric Bogatin

At Nine Dot Connects, we will be the first to admit that Signal Integrity (SI) analysis has not been one of our primary concerns. We believed that following "best practices" would be sufficient for all of our high-speed design needs for years. And it also seemed more cost-effective to do a respin or two rather than spend the money to purchase and learn advanced SI tools.

However, times change, and reality has reared its ugly head. Faster signal transitions, tighter layouts, lower voltage levels, costly high-density parts, and shorter production cycles are all conspiring to make SI analysis an absolute necessity for a successful product.

Lifecycle Insights (September 2018) found that the average number of respins was 2.9, and the average cost of a respin was an incredible $28,482.

In response, we have a webinar to present how SI analysis can be applied to real-world design examples. Tom Cassidy, who has years of experience doing high-speed design and layout, will present a series of common layout paradigms and how SI can be used to identify potential problems and provide solutions. The webinar will culminate with a finished DDR3 design, showing how SI analysis can help ensure a working layout the first time.

Although this webinar will use a board designed in Altium and analyzed in Cadence Sigrity, the concepts apply to any tier-one analysis tool.

Q&A from Webinar

Learn More